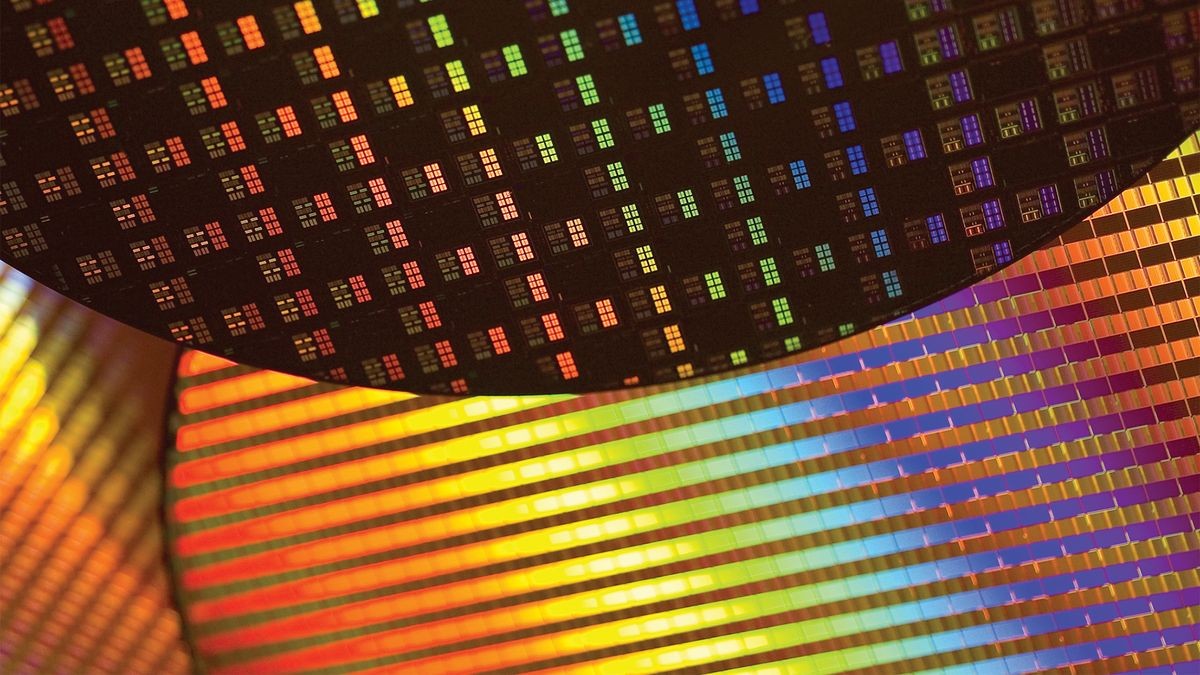

Un empleado de TSMC, identificado como Dr. Kim, reveló recientemente que el equipo de desarrollo logró aumentar en un 6% el rendimiento en la producción de chips de prueba utilizando el proceso de fabricación N2 (clase 2 nanómetros), lo que se traduce en importantes ahorros económicos para los clientes de la compañía.

Este avance llega en un momento clave, ya que TSMC planea iniciar la producción masiva de semiconductores con tecnología N2 durante la segunda mitad de 2025. El proceso N2 marca un hito al ser el primero en implementar transistores de nanohojas gate-all-around (GAA), una innovación que promete reducir el consumo de energía y mejorar el rendimiento.

Los chips fabricados con esta nueva tecnología N2 ofrecerán ventajas notables:

- 25-30% menos consumo de energía

- 10-15% mejor rendimiento

- 15% mayor densidad de transistores

Aunque el Dr. Kim no especificó si la mejora del rendimiento corresponde a chips de prueba SRAM o lógicos, este progreso representa un paso importante. TSMC comenzará a ofrecer servicios de prueba en obleas para la tecnología de 2nm en enero próximo.

Los nuevos transistores GAA nanosheet no solo son más pequeños que sus predecesores FinFET de 3nm, sino que también permiten celdas SRAM de alta densidad más compactas gracias a un mejor control electrostático y menor fuga de corriente.

La compañía taiwanesa, líder mundial en fabricación por contrato de chips, continúa optimizando esta tecnología para reducir la variabilidad y densidad de defectos antes del inicio de la producción masiva prevista para finales de 2025.