TSMC, el gigante taiwanés de la fabricación de semiconductores, presentó esta semana en San Francisco su revolucionaria tecnología de transistores de próxima generación, conocida como N2 o proceso de 2 nanómetros.

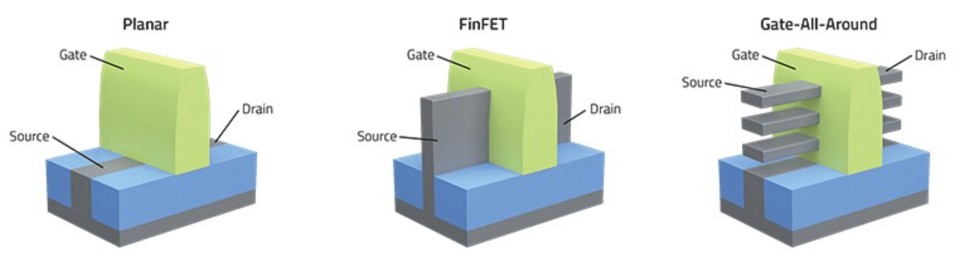

Esta nueva arquitectura, denominada nanosheet o gate-all-around, representa un cambio fundamental respecto a los actuales transistores FinFET. En lugar de utilizar una aleta vertical de silicio, los transistores nanosheet incorporan una pila de cintas estrechas de silicio.

La tecnología N2, resultado de más de cuatro años de investigación y desarrollo, promete mejoras notables en rendimiento: hasta un 15% más de velocidad o un 30% más de eficiencia energética, junto con un aumento del 15% en la densidad de componentes.

Una de las ventajas más destacadas es la flexibilidad que ofrece el diseño nanosheet. La tecnología Nanoflex de TSMC permite crear diferentes celdas lógicas con distintos anchos de nanosheet en el mismo chip. Esto posibilita optimizar áreas específicas: nanosheets estrechos para lógica general y más anchos para núcleos CPU que requieren mayor potencia.

El impacto es particularmente notable en la memoria SRAM, alcanzando una densidad récord de 38 megabits por milímetro cuadrado, un incremento del 11% respecto a la generación anterior.

TSMC planea iniciar la producción en masa de esta tecnología en 2025, al igual que sus competidores Intel y Samsung. Los expertos señalan que la arquitectura nanosheet podría mantenerse como el estándar de la industria durante varios años, con potencial para seguir escalando hasta dimensiones aún más pequeñas.

Esta innovación marca un hito en la evolución de los semiconductores, abriendo nuevas posibilidades para el desarrollo de dispositivos electrónicos más potentes y eficientes.